时钟设计在ASIC和MCU中的关键应用

Table of Contents

在数字集成电路(IC)设计领域,时钟设计是确保芯片功能正常运行的核心要素之一。不论是前端还是后端的工程师,了解时钟信号的来源及其在芯片各个模块之间的分配机制都非常重要。本文旨在深入探讨ASIC(应用特定集成电路)和MCU(微控制单元)中的时钟设计及其应用,全面覆盖从时钟获取到分配的整个过程。

时钟获取的基本方式#

- 外部直接输入时钟信号: 尽管这种方式较少见,主要是因为系统芯片(SoC)中不同功能模块的工作频率需求差异较大,但对于一些非常简单的ASIC项目,外部直接输入时钟信号可能是可行的。

- 外部晶振与内部时钟发生器: 一般情况下,外部晶振连接至芯片的I/O端口,并与内部时钟发生器协同工作,共同生成基础时钟信号,如24MHz,随后供应给各种功能模块。

- 外部晶振、内部时钟发生器加PLL与分频器: 这是现代SoC设计中最常见的时钟生成策略。基本时钟信号从外部晶振获取,并通过PLL(相位锁定环)处理以产生高频时钟信号,然后通过分频器调整,以适应不同模块的频率需求。

时钟设计的实践应用#

在具体的SoC项目中,合理布局和设计时钟系统至关重要。例如,利用多个PLL(如APLL、MPLL、EPLL和VPLL)可以精确控制不同功能模块的时钟需求。由于PLL占用较大的芯片面积,设计初期需要精确评估各模块的时钟需求,以优化PLL的数量和配置,从而节约成本。

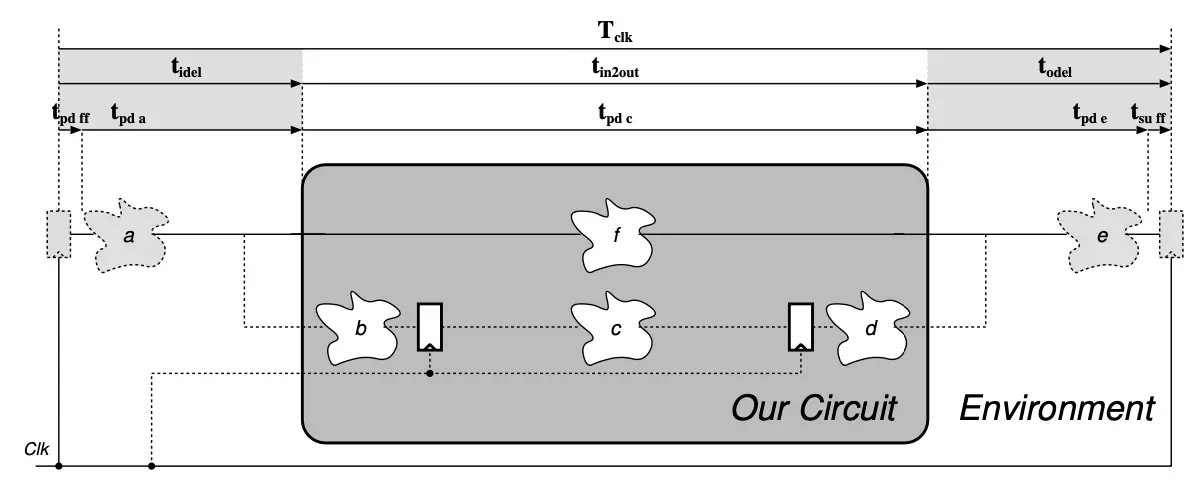

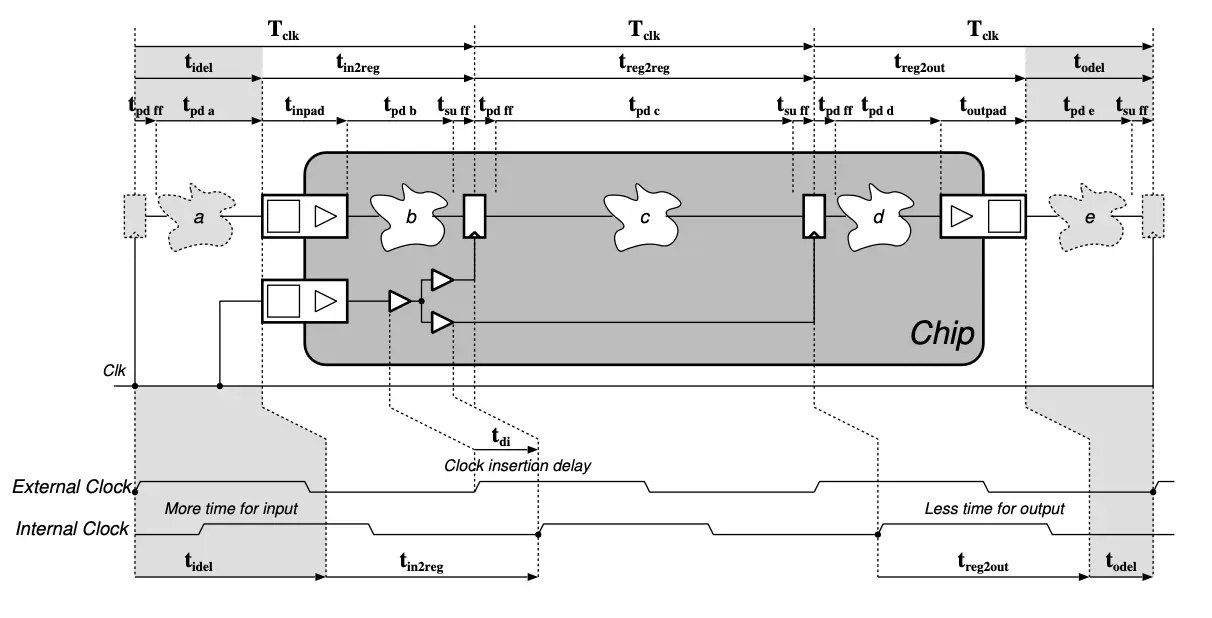

- PLL的位置与时钟树质量: PLL的摆放位置在数字IC后端实现中至关重要,直接影响时钟树的长度,进而影响clock tree latency(时钟树延迟)和clock skew(时钟偏斜)。合理的PLL位置布局可以优化时钟信号的分配,减少时钟延迟和偏斜,确保芯片的高效稳定运行。

时钟综合与模拟#

在时钟设计过程中,使用ICC(集成电路编译器)和DC(Design Compiler)等工具对时钟约束进行前仿和后仿是至关重要的。这些工具帮助设计师优化时钟树,确保时钟信号在设计的各个阶段都能满足性能要求。此外,IOpad的设计也需要考虑时钟信号的分配和布局,以及PLL反馈机制的优化,保证系统的同步性和精确性。

stm32 时钟系统应用#

1. 定时器延时 (HALDelay)#

HALDelay 是许多硬件抽象层(HAL)库提供的一个函数,用于实现阻塞延时。例如,在STM32的HAL库中,HAL_Delay 函数会基于系统的滴答定时器(SysTick)来实现固定时间的延时。

#include "stm32f1xx_hal.h"

int main(void)

{

HAL_Init(); // 初始化HAL库

SystemClock_Config(); // 配置系统时钟

while (1)

{

HAL_GPIO_TogglePin(GPIOB, GPIO_PIN_12); // 翻转GPIO引脚状态

HAL_Delay(1000); // 延时1000毫秒

}

优点:

- 简单易用:直接调用函数,无需复杂配置。

- 相对准确:基于系统时钟,准确性通常足以满足一般应用。

缺点:

- 阻塞操作:在延时期间,CPU不能执行其他任务,效率低下。

- 资源占用:使用系统滴答定时器,可能与其他依赖此定时器的服务(如操作系统时钟)冲突。

2. CPU运算延时 (__NOP() 或 while() 循环)#

这种方法通常涉及在一个空循环中执行一定数量的无操作指令(__NOP())或简单计算,以消耗时间。

void delayMicroseconds(uint32_t microseconds)

{

while(microseconds--)

{

__NOP(); // 执行一个无操作指令,大约持续几纳秒至几十纳秒

}

}

优点:

- 极简实现:不需要任何外部硬件或中断。

- 控制灵活:可以根据需要调整循环次数来微调延时。

缺点:

- 效率低下:CPU在执行无用操作时不能进行其他处理。

- 准确性差:延时的准确性高度依赖于CPU的时钟频率和指令执行时间,难以在不同设备间保持一致。

- 对优化敏感:编译器优化可能会改变延时代码的执行行为。

3. 使用硬件定时器 (Timer)#

#include "stm32f1xx_hal.h"

TIM_HandleTypeDef htim1;

void Timer_Init(void)

{

__HAL_RCC_TIM1_CLK_ENABLE(); // 使能TIM1时钟

htim1.Instance = TIM1; // 定时器实例

htim1.Init.Prescaler = 7200 - 1; // 设置预分频器,使计数器计时频率为10kHz

htim1.Init.CounterMode = TIM_COUNTERMODE_UP; // 向上计数模式

htim1.Init.Period = 10000 - 1; // 设置自动重装载寄存器周期的值

htim1.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1; // 时钟分频因子

HAL_TIM_Base_Init(&htim1); // 初始化定时器

HAL_TIM_Base_Start_IT(&htim1); // 开启定时器并激活中断

}

void HAL_TIM_PeriodElapsedCallback(TIM_HandleTypeDef *htim)

{

if (htim->Instance == TIM1)

{

HAL_GPIO_TogglePin(GPIOB, GPIO_PIN_12); // 在每个周期翻转GPIO引脚状态

}

}

int main(void)

{

HAL_Init();

SystemClock_Config();

Timer_Init();

while (1)

{

// 主循环中其他任务

}

}

硬件定时器利用微控制器内置的定时器模块来计时,可以配置为一次性或周期性触发。

优点:

- 非阻塞:CPU可以在定时器计时期间执行其他任务,提高程序的效率。

- 高精度和可靠性:定时器的准确性不受CPU主频影响,适用于要求严格的时间控制。

- 灵活性:可以配置为触发中断,执行特定的中断服务程序,适合复杂的时间管理任务。

缺点:

- 配置复杂:相较于简单的延时函数,使用硬件定时器需要更多的初始化和配置。

- 资源占用:可能会占用有限的定时器资源,与其他需要使用定时器的功能产生冲突。

结论#

选择哪种计时方法取决于具体的应用需求:

- 对于非关键任务,可以选择简单的

HALDelay或CPU运算延时。 - 对于需要高精度和非阻塞操作的应用,建议使用硬件定时器。

Related

ML边缘部署

152 words·1 min·

loading

·

loading

new

docs

RISCV ISA 入门

63 words·1 min·

loading

·

loading

new

docs

MCU的启动分析

162 words·1 min·

loading

·

loading

new

docs

环境配置入门

40 words·1 min·

loading

·

loading

new

docs

VlSI1回顾: FPGA组成 与 Dedicated Processor 架构

309 words·2 mins·

loading

·

loading

new

docs